Summary

MARMOT RISC-V ASIC is MCU with a large memory e.g. megabytes leveraging external QSPI flash and PSRAM giving the programmer large workspace so she or he can perform over-the-air firmware upgrade. We noted that each QSPI memory access takes ~100 internal clock cycles. In this design 16KB i-Cache and 8KB d-Cache is there to alleviates this slow access of QSPI memories. Furthermore we added 3-channel PWMs so 3-phase BLDC motors can be driven.

Large Memories with Protection

The Marmot RISC-V ASIC provides larger real memories (mega bytes) than typical microcontroller (10s and 100s of kilo bytes). The RISC-V CPU does not offer Memory Management but offers Physical Memory Protection (PMP) which can allow or disallow memory accesses by user, libraries and systems. The PMP with appropriate software can provide protection on assets (e.g. code and data).

How Physical Memory Protection (PMP) Relates to RTOS Code

Present RTOSes do not have features that can exploit PMP. On the other hand one can add code to those RTOSes to leverage PMP and make user program unable to invate operating system code and data.

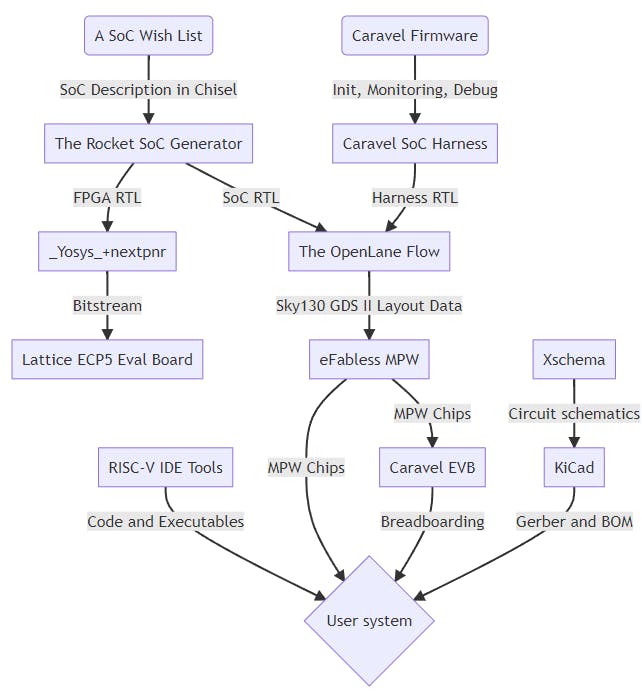

Hardware and Software System Build

The following figure shows how the hardware and software pieces are merged into one coherent system. The Rocket SoC Generator, based upon the hardware description written in Chisel language, automatically outputs CPU, buses, memories and peripheral I/Os. Memory and I/O address maps are created in the process. The Rocket output logic is stitched with Caravel harness logic to make up the ASIC. The ASIC functions can be pre-validated using an FPGA prior to commitment to a silicon. The board designed with an open source board design EDA tool KiCAD. The software is developed and debugged on the breadboard and integrated into the final system using the debug ICE interface.

Example User System Marmot ASIC is Applied to

The following system shows an example of the User system. This version shows breadboarding arrangements where evaluation boards of the major components were purchased and hand solidered into a single system. Caravel evaluation boards will become one of the breadboards where the software in each SoC/MCU is debugged to constitute one system function.

System Bringup Sequence

The figure below shows the way how System, Harness, Caravel SoC (CPU), Rocket SoC (CPU) are brought up as a single system. Once system power is up first eFabless harness goes through a power on reset (POR). This brings up the Caravel SoC, which finallly brings up Rocket SoC. Caravel firmware (initially in external SPI flash) can go back to reinitialize clock, DLL, GPIO routing and user clock (the clock goes to Rocket SoC). After this Rocket SoC software can control system clock which is fed to the Rocket/Caravel SoC.

Learing Curve: MPW-7 vs. MPW-6

OpenLane EDA, OpenRAM, OpenPDK each has learning curves. Hence 2X in clocking, 1.5X in amount of cache memories.

50MHz = MPW-7 = MPW-6 x 2 in Clocking

24KB = MPW-7 = MPW-6 x 1.5 in I/D Cache

Addition of PMP logic, PWM logic were achieved.

This is after maybe one hundred times of global place and route practices.

MPW-6 MPW-7

Conclusions

After tons of running EDA tools, OpenRAM and OpenLane tools, more skills and tricks were acquired. This doubled the clocking (25MHz > 50MHz), 50% increase in cache size (16KB > 24KB) and additional logic (PMP, PWM etc.). Below is pictures of MARMOT systems sunbathing in the rooftop of Vietnam waiting for the MPW-6 silicon /evb to show up.

Acknowledgements

This work is based on results obtained from project, JPNP16007, commissioned by The New Energy and Industrial Technology Development Organization (NEDO).

Increased features (plus 8KB D-Cache and 3ch PWM)and improved clocking (25MHz > 50MHz) by mastering tools since MPW-6 MARMOT RISC-V, three months ago.

processor

sky130A