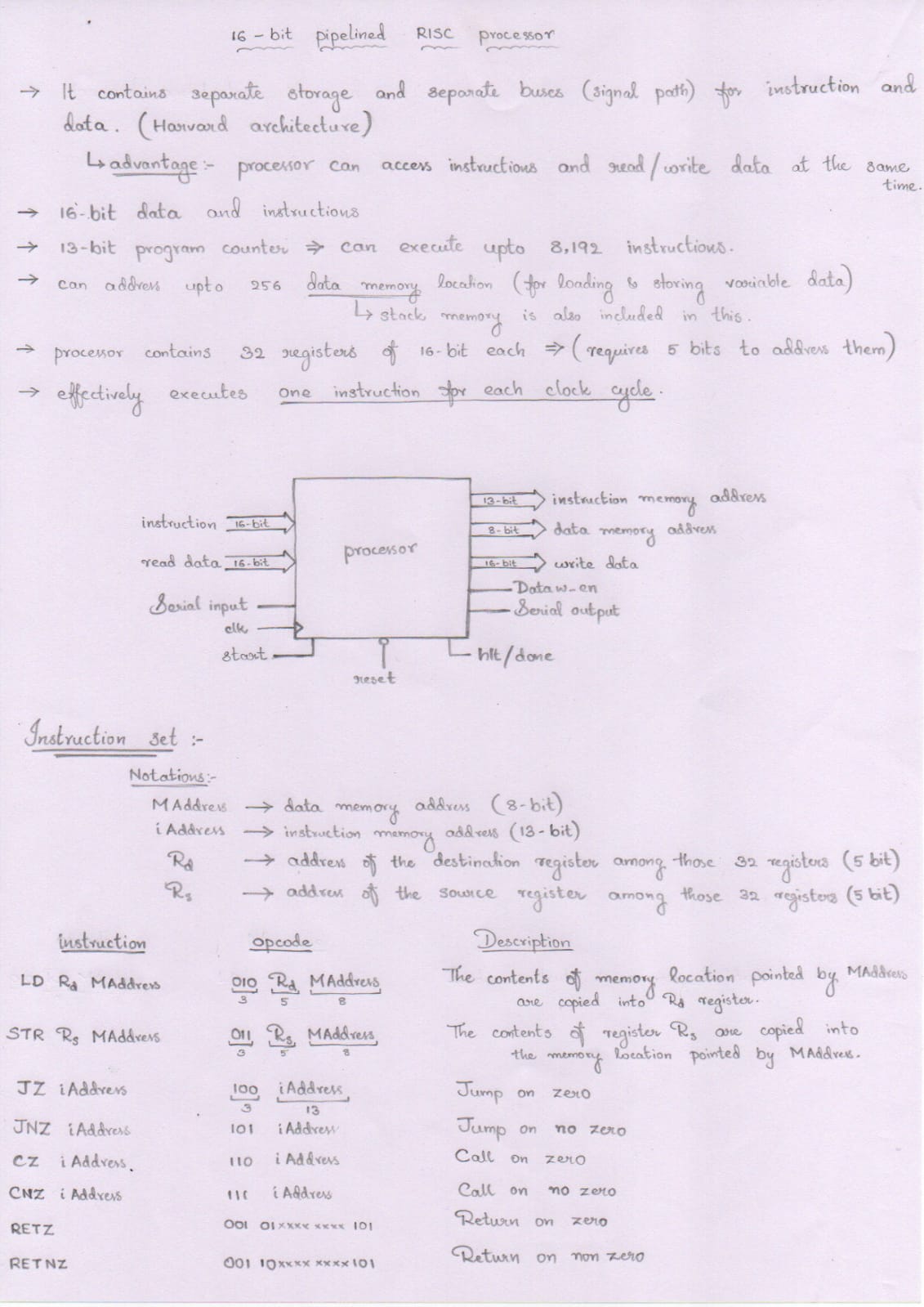

- Developed a new Reduced Instruction Set with least possible no. of instructions in it such that the designed Processor can be used to implement almost any Function by combination of instructions

- Implemented the Processor using Verilog HDL in Xilinx Vivado

- In the process of Designing the processor, I have implemented many smaller components like 16-bit adder, Decoders, Register file, Stack Pointer, Program Counter, ALU and finally integrating everything as processor by designing Control Unit, buses, instruction registers, etc

- Using the concept of pipelining divided execution of instruction in several stages such that approximately one instruction is executed for every clock cycle

7vik-g/-16bit-pipelined-RISC-processor-mpw8

This commit does not belong to any branch on this repository, and may belong to a fork outside of the repository.

Folders and files

| Name | Name | Last commit message | Last commit date | |

|---|---|---|---|---|

Repository files navigation

About

No description, website, or topics provided.

Resources

License

Stars

Watchers

Forks

Releases

No releases published

Packages 0

No packages published