The repo contains the FPGA layout integration with the Caravel chip. The content of the repo represents the first generation version of CLEAR delivered by @Manarabdelaty of efabless

CLEAR is an Open Source FPGA ASIC delivered to you on its development board and its open source software development tools and all the ASIC design tools used to create it. That's for you to create your own - yes that's right - ASIC.

CLEAR is utilizing Caravel - the open source ASIC platform provided as a base System on Chip (SoC) provided by Efabless' chipIgnite offering.

- Generate an embedded FPGA macro based on the famous OpenFPGA generator framework

- Integrate the eFPGA macro into Caravel which makes it an FPGA ASIC - Clear

- Manufacture the ASIC through chipIgnite program through SkyWater Technology

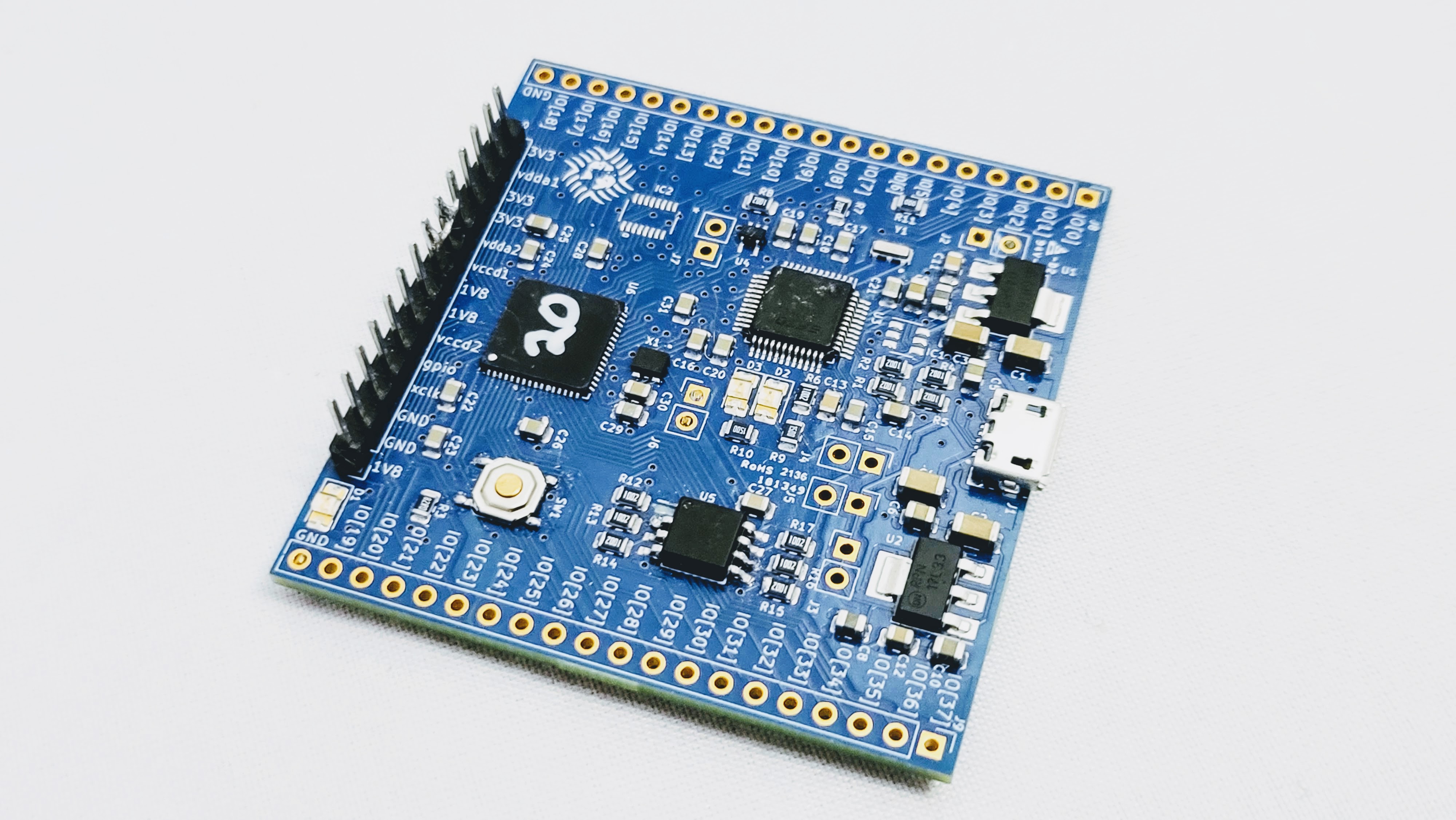

- Package and mount the ASIC on its development board

- Test the boards before you get them along with the open source FPGA programing software

- You receive your board and have fun!

As part of the campaign we will show you everything we do including how to design your own ASIC with open source ASIC design software and how you can create a campaign just like this one for your own custom ASIC. All that without having to make a giant hole in your pocket for ASIC design and manufacturing.

- CNX Software - CLEAR is an open-source FPGA ASIC provided by Efabless’ chipIgnite

- hackster.io - Efabless' CLEAR Is a Fully Open Source ASIC with Embedded FPGA and RISC-V Core, Now on GroupGets

- 100% Open Source FPGA ASIC

- A small but not-so-little 8x8 (64) CLB eFPGA

- CPU Subsystem

- Peripherals

- SPI master

- UART

- 39 software configurable GPIO

- Counter/Timers

- Logic Analyzer

- Additional features

- Programmable internal clock frequency

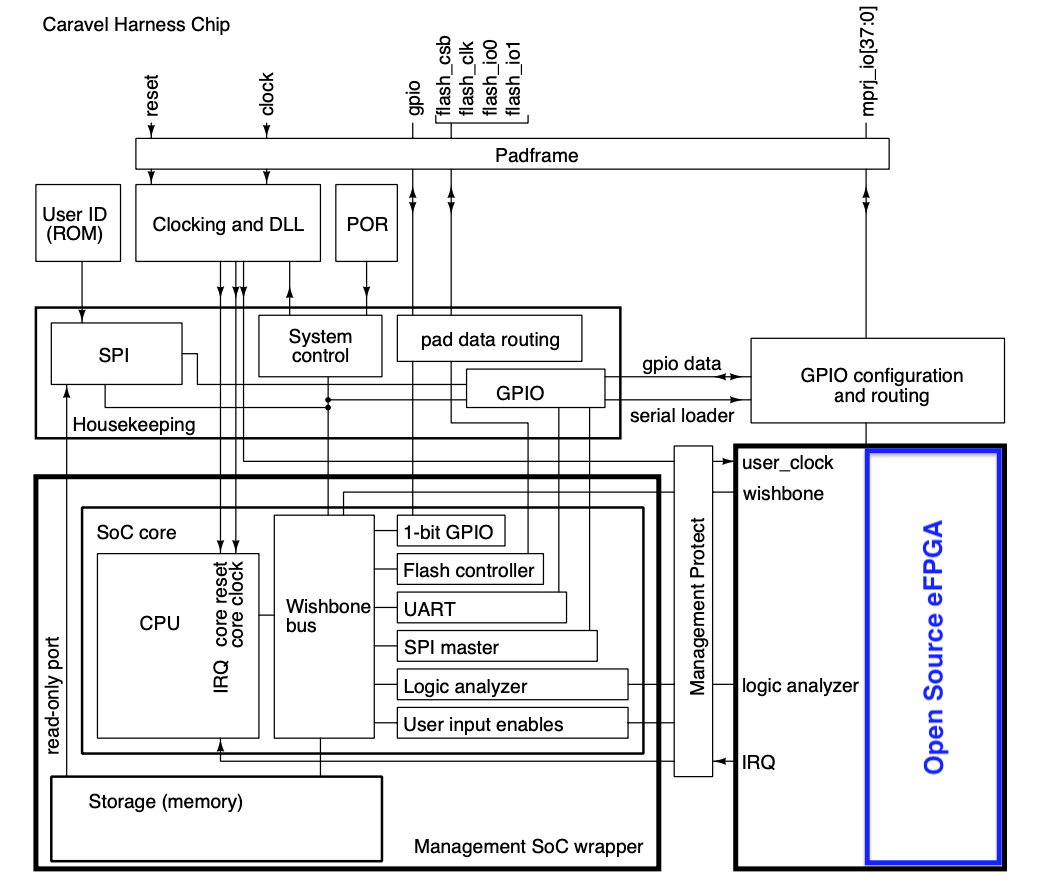

CLEAR - Block Diagram

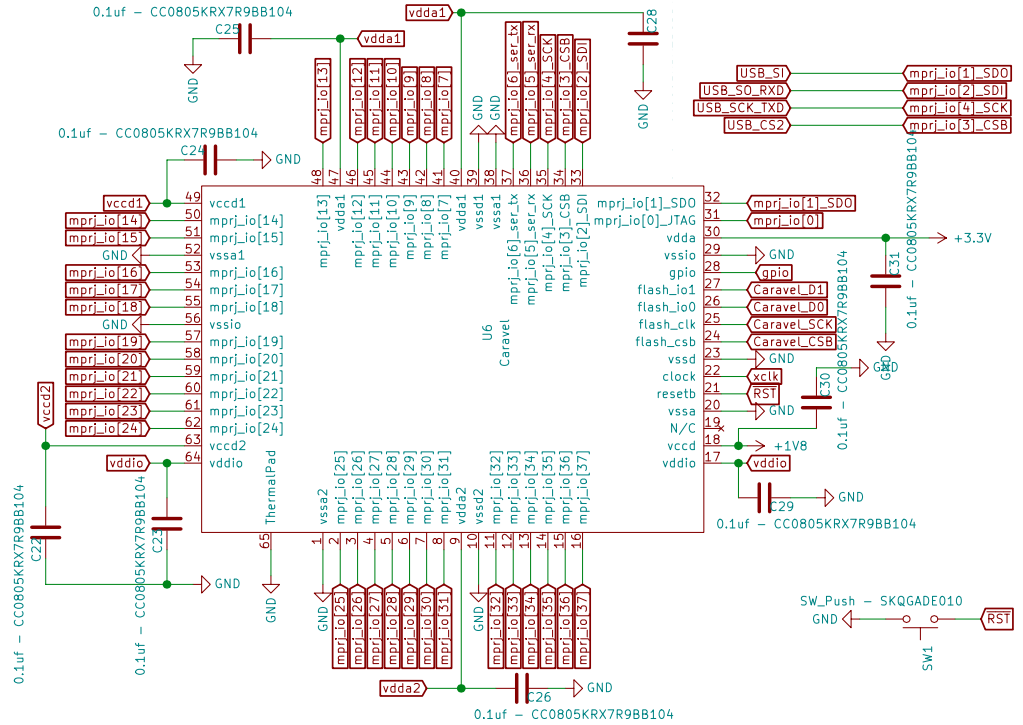

CLEAR - ASIC Pinout

If the April shuttle does not go out, then the June chipIgnite shuttle will be used which extends delivery to November.

The layout is an 8x8 FPGA fabric generated using OpenFPGA and hardened using OpenLane.

The 8x8 fpga interface to the managent area can be found at user_project_wrapper.v . The fabric is conncted to the managemtent area logic analyzer, wishbone bus, and IO-ports.

| Caravel-IO | FPGA | Mode |

|---|---|---|

| io[0] | test_en | Input |

| io[1] | IO_ISOL_N | Input |

| io[7:2] | EMBED-IO[10:15] | Bi-directional |

| io[11] | sc_tail | Output |

| io[12] | ccff_head | Input |

| io[13:14] | EMBED-IO[8:9] | Bi-directional |

| io[17:23] | EMBED-IO[1:8] | Bi-directional |

| io[24] | EMBED-IO[0]* | Bi-directional |

| io[25] | wb_la_switch | Input |

| io[26] | sc_head | Input |

| io[27:34] | EMBED-IO[88-95] | Bi-directional |

| io[35] | ccff_tail | Output |

| io[36] | clk | Input |

| io[37] | prog_clk | Input |