CLEAR is an open-source FPGA ASIC delivered on a development board, accompanied by open-source software development tools and ASIC design tools. This comprehensive package enables you to create your own ASIC.

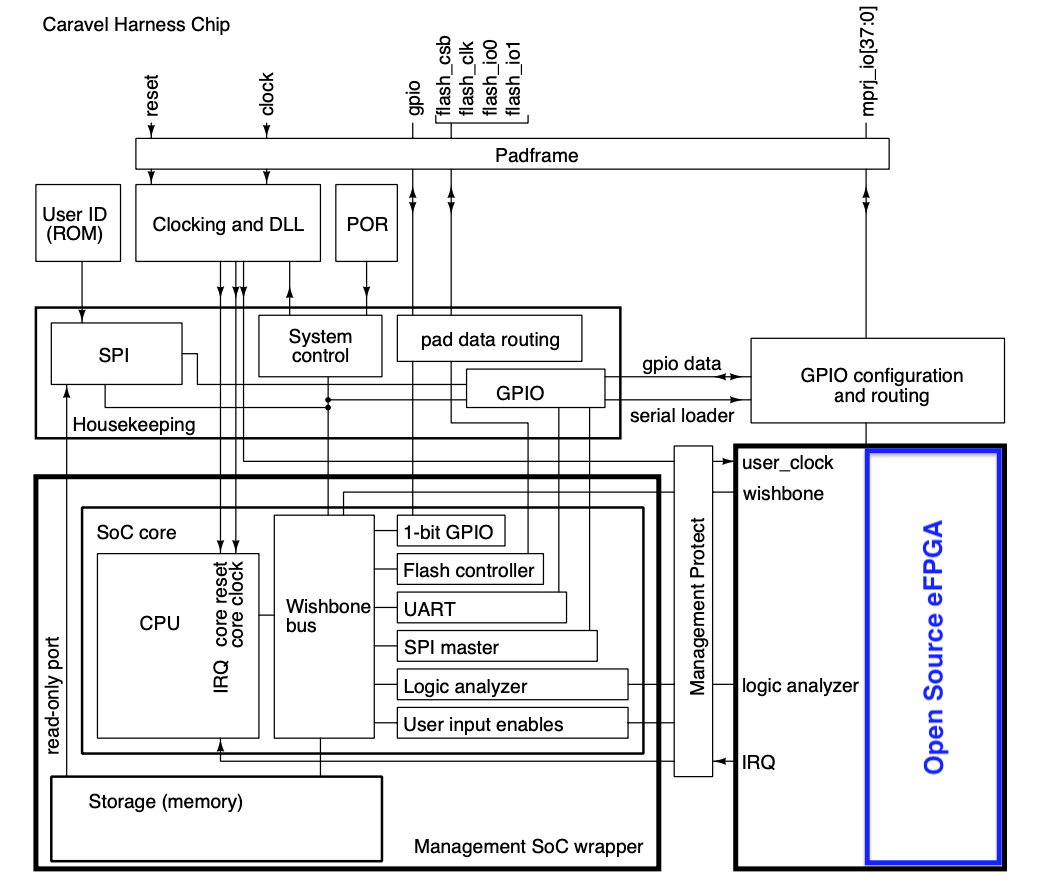

CLEAR utilizes Caravel, an open-source ASIC platform provided by Efabless' chipIgnite offering.

The FPGA fabric is generated using OpenFPGA and hardened using OpenLane.

The table below details the I/O connections between Caravel and the user project, indicating the functionality and corresponding pins for each connection.

| IOs | Clear |

|---|---|

| mprj_io[0] | FPGA IO[46] |

| mprj_io[1] | HK SDO - FPGA isol_n |

| mprj_io[2] | HK SDI - FPGA IO[45] |

| mprj_io[3] | HK CSB - FPGA IO[44] |

| mprj_io[4] | HK SCK - FPGA IO[43] |

| mprj_io[5] | UART RX - FPGA IO[42] |

| mprj_io[6] | UART TX - FPGA IO[41] |

| mprj_io[7] | irq - FPGA IO[40] |

| mprj_io[8] | FPGA IO[39] |

| mprj_io[9] | FPGA reset |

| mprj_io[10] | FPGA test_enable |

| mprj_io[11] | FPGA IO[38] |

| mprj_io[12] | FPGA IO[37] |

| mprj_io[13] | FPGA IO[36] |

| mprj_io[14] | FPGA sc_tail |

| mprj_io[15] | FPGA IO[19] |

| mprj_io[16] | FPGA IO[18] |

| mprj_io[17] | FPGA IO[17] |

| mprj_io[18] | FPGA IO[16] |

| mprj_io[19] | FPGA IO[15] |

| mprj_io[20] | FPGA IO[14] |

| mprj_io[21] | FPGA IO[13] |

| mprj_io[22] | FPGA sc_head |

| mprj_io[23] | FPGA ccff_tail |

| mprj_io[24] | FPGA IO[127] |

| mprj_io[25] | FPGA IO[126] |

| mprj_io[26] | FPGA IO[125] |

| mprj_io[27] | FPGA IO[124] |

| mprj_io[28] | FPGA IO[123] |

| mprj_io[29] | FPGA prog_reset |

| mprj_io[30] | FPGA IO[122] |

| mprj_io[31] | FPGA IO[121] |

| mprj_io[32] | FPGA IO[120] |

| mprj_io[33] | FPGA IO[119] |

| mprj_io[34] | FPGA ccff_head |

| mprj_io[35] | FPGA clk_sel |

| mprj_io[36] | FPGA clk |

| mprj_io[37] | FPGA prog_clk |

The RISC-V CPU is connected to FPGA I/Os through logic analyzers, facilitating communication between the FPGA and RISC-V.

| FPGA IOs | Logic Analyzers |

|---|---|

| gfpga_pad_io_soc_in[47] | la_data_out[127] |

| gfpga_pad_io_soc_in[48] | la_data_out[126] |

| gfpga_pad_io_soc_in[49] | la_data_out[125] |

| ... | ... |

| gfpga_pad_io_soc_in[117] | la_data_out[57] |

| gfpga_pad_io_soc_in[118] | la_data_out[56] |

For more detailed steps and further information, please visit the GitHub repository.

CLEAR

Efabless

Silicon Services

Free