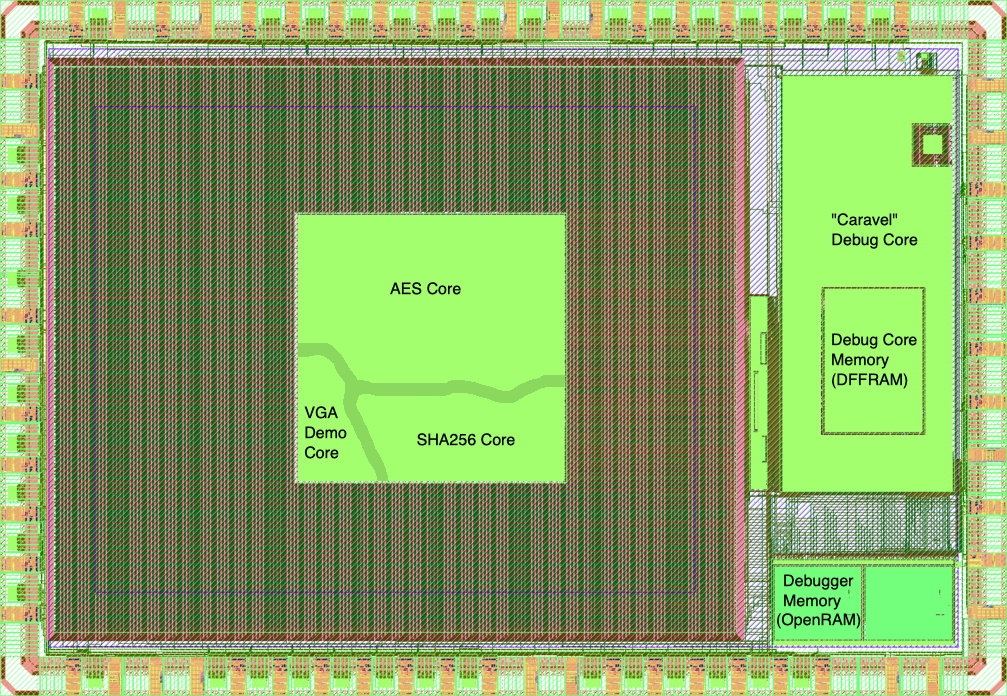

This is a cryptography accelerator ASIC designed using the SKY130 (130nm) process node, to be taped out on the Google/Skywater/efabless open-source MPW shuttle. It includes hardware implementations of cores for AES128/AES256 and SHA256, as well as an experimental VGA-based game demo (it also includes the "caravel" debug-harness/padframe which is being used in this tapeout). The eventual goal of this project is to use it for embedded/IoT security applications.

This repository (asinghani/crypto-accelerator-builds) contains the openlane-based build environment (including the final tapeout-ready GDS files). It contains the main project repository (asinghani/crypto-accelerator-chip) as a submodule and uses symbolic links to form the directory structure (this is done to keep the main project repository cleaner, as this repository is quite unwieldy to manipulate due to its size). The build products must be stored inside this repo in order to use it with the efabless Open MPW platform, which pulls the build products directly from the git repository.

When working with the design, this repository must always be used as it contains fundamental parts of the build environment.

The accelerator itself (which is designed to be usable on both FPGA and ASIC) is designed in Chisel3 and is at asinghani/crypto-accelerator (it is also submoduled into this repository to make builds easier).

This chip contains 4 major components:

AES128/256 Accelerator

SHA256 Accelerator

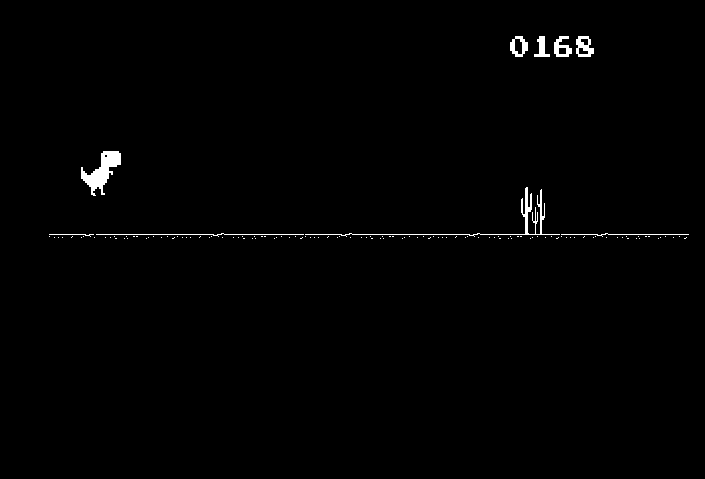

VGA Game Demo (experimental)

crypto_accelerator.v file that is already in the repository)```sh

git clone --recurse-submodules https://github.com/asinghani/crypto-accelerator-builds

make uncompress ```

To run the tests (both RTL-level and gate-level):

```sh cd verilog/dv/caravel/accelerator/

cd

accelerator directory):make rtl # RTL tests make gl # gate-level tests ```

The aes and sha256 testbenches are self-checking, and will print failure messages if there are any issues. There are additional verification steps in the Chisel3 testbenches (in the crypto-accelerator repo), including several hundred more test cases.

The dino_vga test is special because it cannot be automatically verified. Instead, there is a python script in the dino_vga directory (named parse.py, with numpy, vcdvcd, and opencv-python modules as dependencies) which can be invoked (from inside the dino_vga directory) as python3 parse.py dino_vga.vcd "dino_vga_tb.dump[40:0]" to parse the VCD and generate a PNG file frame.png containing the VGA frame outputted by the design (which can be visually inspected for correctness).

(Expects that the download procedure has been completed, including the uncompress stage)

```sh

cd crypto-accelerator-chip && ./update-verilog.sh && cd ..

cd openlane && make accelerator_top && cd .. ls openlane/accelerator_top/runs/ # Find the most recent run name

./migrate-accel-gds.sh

cd openlane && make user_project_wrapper && cd ..

./migrate-gl.sh

make ship

gds/caravel.gds./render.sh # May need to run with XVFB if in a headless environment ```

The relevant files in this repository are as follows (the caravel harness files are excluded here, see details about them in efabless/caravel):

``` add_spdx.py - Script to add SPDX license identifiers to source files compress.py - Compress large build products using gzip to fit into GitHub repo size limit crypto-accelerator-chip - Submodule which contains the main source code (no build products) └─crypto-accelerator - Submodule which contains the Chisel3 design for the crypto accelerator

def - Post-routing DEF build files (for the accelerator as well as the caravel harness)

gds - Final GDS files (for the accelerator as well as the caravel harness)

info.yaml - Metadata used by efabless platform for tapeout

lef - Abstracted LEF views (for the accelerator as well as the caravel harness)

mag - Magic build files (for the accelerator as well as the caravel harness)

maglef - Abstracted magic build files (for the accelerator as well as the caravel harness)

Makefile - Script to build the final "ship" product for caravel

migrate-accel-gds.sh - Script to transfer the GDS files after running an openlane build

migrate-dv.sh - Script to re-build the directory structure in verilog/dv/caravel/accelerator

migrate-gl.sh - Script to transfer the gate-level netlists to be used for gate-level simulations

ngspice - Simulations of the analog blocks in the caravel harness

openlane

├─accelerator_top - Configuration for building the main accelerator block

└─user_project_wrapper - Configuration for building the "wrapper" block which is used to fit the accelerator into the harness

qflow - Analog components from the caravel harness render.py - KLayout script to generate a top-level render of caravel.gds render.sh - Shell script to invoke KLayout and load render.py to generate the render scripts - Various scripts used to prepare the chip for tapeout spi - LVS extraction files utils - Various scripts to handle file format conversions verilog ├─dv │ └─caravel │ └─accelerator │ ├─aes - Test cases for the AES128/256 core │ ├─dino_vga - Simulation for the VGA game demo (must be verified visually) │ ├─Makefile - Runs all simulations │ └─sha256 - Test cases for the SHA256 core │ ├─rtl │ ├─accelerator │ │ ├─accelerator_top.v - Top-level design, instantiates and connects all the relevant modules │ │ ├─crypto_accelerator.v - Crypto accelerator verilog (auto-generated from Chisel3 RTL design) │ │ └─dino - Directory which contains all the sources for the VGA game demo │ │ │ │ │ └─user_project_wrapper.v - Instantiation of the accelerator core (exposing relevant ports to caravel) │ ├─gl - Autogenerated gate-level models of each of the modules └─stubs - Stubs for LVS on analog components of caravel harness ```

ASIC containing a combined AES128/256 accelerator core and a VGA graphics/game demo

1.00

Accelerator

sky130A