Successive-approximation-register (SAR) analog-to-digital converters (ADCs) are ubiquitous in general applications including sensor networks, battery-powered devices and control systems due to their notable energy efficiency [1]. As a result, this ADC architecture comprises the majority of ADC needs for medium- to high-resolution converters in the range of 8-18bit resolution with sample rates on the order of 5Msps [2]. This demand has been recognized and proposed for the sky130 node [3,4]. As of 2022, SAR designs with 8-bit resolution have been proposed [5], however a community need has been declared for 12-bit resolution [4].

This project aims to support the goals of IEEE SSCS and the growing community surrounding the sky130 node with two primary design goals:

1) push useful, open IP designs for the sky130 node towards higher resolution ADCs using recent, exciting design techniques [6] and

2) unite university groups with limited IC design experience with experienced mentors to benefit from the collaboration opportunities enabled by the rapidly growing open-source IC design movement [3].

To these ends, Dr. Phillip Bailey of MIT Lincoln Laboratory Group 86 will guide Assistant Professor Dr. Aubrey Beal and undergraduate student Micah Tseng at the University of Alabama in Huntsville (UAH) Department of Electrical and Computer Engineering (ECE) in the design of a 10-bit SAR ADC similar to [6] for the sky130 node. This particular design has been chosen for its overlap of usefulness to the community and instructive potential for mixed-signal ASIC design.

The resulting design experience, hardware and testing will be leveraged to construct a new ECE elective course at UAH entitled EE410/510 Open-source IC Design planned for Spring 2023. This course will be open to both undergraduate and graduate students in Electrical and Computer Engineering programs with the aim that student projects will use tools, models and workflow compatible with the sky130 node.

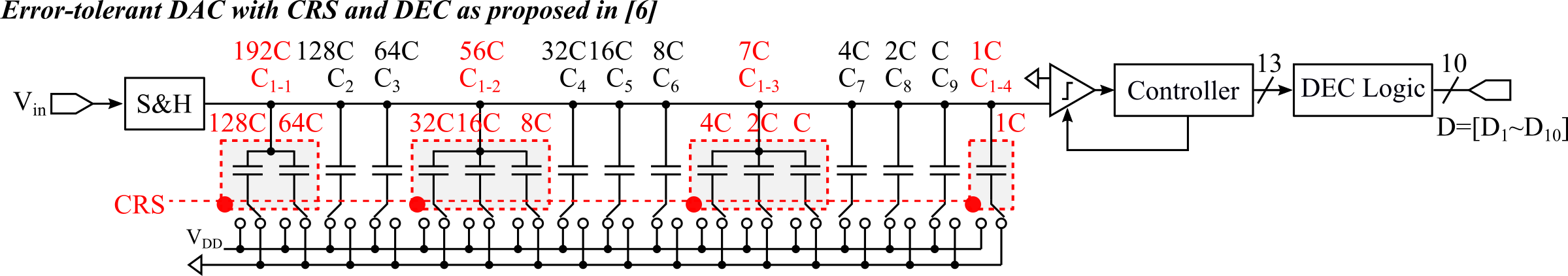

Performance indexes for ADCs are closely linked to the digital-to-analog converter (DAC) subsystem designed within the ADC's feedback loop. One recent, notable approach [6] reported an impressive Walden figure-of-merit (FOM) that overcame bottlenecks in ADC design in terms of energy, speed, resolution (effective number of bits or ENOB) and area. The design proposed for this project utilizes DAC innovations described in [6] that reportedly improve DAC linearity by 1 bit (coined as correlated-reversed switching or CRS) and allow for wide error-tolerance ranging with no redundant capacitors through the use of addition-only digital error correction (DEC).

In this design, we propose an analog-to-digital converter (ADC) consisting of 4 subsytems that achieve a successive-approximation of its input voltage via hardware implementation of a binary search algorithm. At the input, a sample-and-hold (S/H) circuit consists of a MOSFET switch, capacitor and bootstrap circuit [6] that allows analog inputs to make use of (nearly) rail-to-rail supply voltage swing for signals presented to its input [7,8]. A comparator circuit follows the S/H stage and consists of a preamplifier followed by a differential latch circuit [9]. Finally, a control loop that consists of a capacitive digital-to-analog converter (DAC) and corresponding control logic allows a successive-approximation-register (SAR) subcircuit to output a digital code that approximates a voltage presented at the input of the ADC. Importantly, the DAC in this design will utilize CRS and DEC improvements as shown in [6], however, our design will be clocked instead of asynchronous for ease of implementation. The result is an ADC architecture that is calibration free, error correcting and supports input ranges near the power rails.

| VDD | 1.8V |

| Power | <1mW |

| Sample Rate | 5Msps |

| ENOB | >8 Bits |

| Target Input Range | -1.8V to +1.8V |

[1] Baker, R. Jacob. CMOS: circuit design, layout, and simulation. John Wiley & Sons, 2019.

[2] Maxim Integrated, “Tutorial on Successive Approximation Registers (SAR) and Flash ADCs,” Application Note 1080, Oct. 2001

[3] “2022 SSCS ‘pico’ open-source Chipathon,” IEEE Solid-State Circuits Society. [Online]. Available: https://sscs.ieee.org/about/solid-state-circuits-directions/sscs-pico-design-contest. [Accessed: 25-Apr-2022].

[4] kassemmkk, (2022) SkyWater (SKY130) Open Source Program IP Catalog [Online Repository]. https://github.com/efabless/skywater-pdk-central/blob/main/design-ip.md

[5] chrische-xx, (2021) 8-bit SAR-ADC with offset calibration [Online Repository]. https://github.com/chrische-xx/caravel_user_project_analog

[6] Tsai, Jen-Huan, et al. "A 0.003 mm2 10 b 240 MS/s 0.7 mW SAR ADC in 28 nm CMOS With Digital Error Correction and Correlated-Reversed Switching." IEEE Journal of Solid-State Circuits 50.6 (2015): 1382-1398.

[7] Abo, Andrew M., and Paul R. Gray. "A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter." IEEE Journal of Solid-State Circuits 34.5 (1999): 599-606.

[8] Razavi, Behzad. "The bootstrapped switch [a circuit for all seasons]." IEEE Solid-State Circuits Magazine 7.3 (2015): 12-15.

[9] Miyahara, Masaya, et al. "A low-noise self-calibrating dynamic comparator for high-speed ADCs." 2008 IEEE Asian Solid-State Circuits Conference. IEEE, 2008.

1. Dr. Phillip Bailey (Team Lead) - Group 86, MIT Lincoln Laboratory

Dr. Phillip Bailey is a technical staff member in the RF Technology Group. His research interests include mixed signal circuits, digital beamforming, and applications of chaos in electronic circuits. Prior to joining the Laboratory, Dr. Bailey worked as a graduate student at Auburn University, where his work focused on the mixed signal implementation of exactly solvable chaotic systems. He also performed research on high-speed interconnects and microwave calibration structures. Dr. Bailey has authored or coauthored a number of journal and conference publications in the fields of digital interconnects and chaos. He received his BEE, MS, and PhD degrees in electrical engineering from Auburn University.

2. Dr. Aubrey Beal (Academic Advisor) - Assistant Professor, Department of Electrical & Computer Engineering, The University of Alabama in Huntsville

Dr. Beal received his Ph.D. degree in Electrical Engineering from Auburn University. His research uses concepts in nonlinear dynamics to innovate techniques for communication systems, compressive noise ranging systems and true random number generation in integrated circuits. As a postdoctoral researcher with the U.S. Department of Energy's Oakridge Institute for Science and Education he applied these concepts to give unique advantages to physical systems. Before becoming an Assistant Professor at UAH, Dr. Beal was a civil servant researcher with the U.S. Army RDECOM (now Futures Command CCDC) Charles M. Bowden Laboratory at Redstone Arsenal. This work supported early basic and applied research. His current research interests highlight the intersection of nonlinear dynamics and engineering applications to support advances in signal processing, sensing, security and machine learning.

3. Micah Tseng (Undergraduate Student) - Department of Electrical & Computer Engineering, The University of Alabama in Huntsville

Micah Tseng is an undergraduate student at the University of Alabama in Huntsville. As an Undergraduate Research Assistant at the University of Alabama in Huntsville, he worked on an NSF funded research project designing a control and feeding network for a digital beamformer to test phased array antennas. Additionally, Micah Tseng currently works as a freelance live audio engineer designing and operating live sound reinforcement systems for Fortune 1000-500 companies and large music concerts. His current research interests use nonlinear dynamics, information theory and machine learning to inform new transmission and processing techniques in communications with a special interest towards live audio systems.

This project aims to create a 10 bit SAR ADC with the goals of extending useful mixed-signal IP for the sky130 node and educating emerging IC designers. This will be a collaborative effort between MIT Lincoln Labs IC designers and UAH faculty/undergraduate students. The results will open SAR ADC designs as well as material for an upcoming undergraduate/graduate course in open-source IC design to be offered at UAH in Spring 2023.

0.0.1

adc