Integrated Circuits (ICs) have become more vulnerable to faults and errors such as those introduced by ionizing radiation and by electrostatic and -magnetic interference. Given ICs’ ubiquity in critical systems (e.g., autonomous systems, military/space systems), soft error mitigation approaches are necessary–but ones that alter the hardware are more expensive, perform more poorly, and require longer fabrication time. This project aims to improve reliability by exploiting masking properties within conventional design flows to build a reliability-aware microcontroller that will reduce, eliminate, and/or otherwise mitigate soft faults and errors in off-the-shelf ICs for critical applications.

The goal of this project is to mitigate soft errors by exploiting masking properties within the RTL-to-GDSII design flow. The design flow will be used to build a series of reliability-aware microcontrollers using the various reliability-aware design techniques, including:

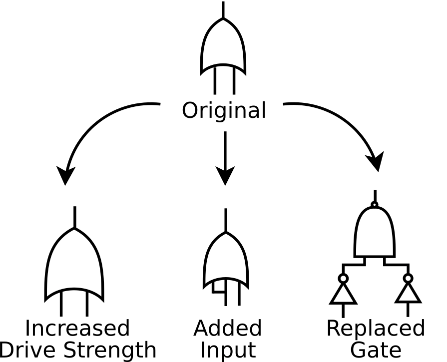

An example of gate replacement strategies to mitigate single event transients is shown in the figure below:

The design will be tested through simulation, using code emulating upsets, and experimentation, using pulsed-laser fault injection techniques. Results from the laser fault injection tests will provide insight into the effectiveness of radiation-hardened-by-design mitigation techniques. Since the design will be fabricated in an open-source technology, exact locations of strikes can be identified.

A basic block diagram of the proposed chip is shown below and was adapted from the project "Riscduino QCore" (https://platform.efabless.com/projects/782)

RTL taken from Riscduino SOC Integrated Quad 32 Bits RISC V core (https://platform.efabless.com/projects/782) which was adapted from Syntacore SCR1 (https://github.com/syntacore/scr1)

Performance numbers are expected to be similar for certain metrics but not match since there will be added components and customized synthesis, placement, and routing.

Automated Design for Emerging Processing Technologies (ADEPT) Laboratory

at North Carolina A&T State University

https://sites.google.com/view/adept-laboratory

[1] Daniel B. Limbrick, Nihaar N. Mahatme, William H. Robinson, and Bharat L. Bhuva, “Reliability-Aware Synthesis of Combinational Logic With Minimal Performance Penalty,” IEEE Transactions on Nuclear Science, Vol. 60, No. 4, pp. 2776-2781, 2013.

[2] Bradley T. Kiddie, William H. Robinson, and Daniel B. Limbrick, “Single-Event Multiple-Transient Characterization and Mitigation via Alternative Standard Cell Placement Methods,” ACM Transactions on Design Automation of Electronic Systems, Vol. 20, No. 4, pp. 1-22, 2015.

[3] Zhou, M. R. Choudhury, and K. Mohanram, “Tunable transient filters for soft error rate reduction in combinational circuits,” in 2008 13th European Test Symposium, pp. 179–184, IEEE, 2008.

[4] M. Andjelkovic, O. Schrape, A. Breitenreiter, J. Chen, and M. Krstic, “A tunable single event transient filter based on digitally controlled capacitive delay cells,” in 2021 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pp. 1–6, 2021

Multiple microcontroller cores will be placed on the same die, each with a reliability-aware enhancement in the design process (e.g., synthesis, floorplanning, placement, routing) to identify the most cost effective way to mitigate soft errors.

1

processor